### **General Description**

The MAX3841 is a low-power, 12.5Gbps 2 × 2 crosspoint switch IC for high-speed serial data loopback, redundancy, and switching applications. The MAX3841 current-mode logic (CML) inputs and outputs have isolated V<sub>CC</sub> connections to enable DC-coupled interfaces to 1.8V, 2.5V, or 3.3V CML ICs. Fully differential signal paths and Maxim's second-generation SiGe technology provide optimum signal integrity, minimizing jitter, crosstalk, and signal skew. The MAX3841 is ideal for serial OC-192 and 10GbE optical module, line card, switch fabric, and similar applications.

The MAX3841 has 150mV<sub>P-P</sub> minimum differential input sensitivity, and 500mV<sub>P-P</sub> nominal differential output swing. Unused outputs can be powered down individually to conserve power. In addition to functioning as a 2 × 2 switch, the MAX3841 can be configured as a 2:1 multiplexer, 1:2 buffer, or dual 1:1 buffer. The MAX3841 is available in a 4mm × 4mm 24-pin thin QFN package. and consumes only 215mW with both outputs enabled.

### **Applications**

OC-192, 10GbE Switch/Line Cards OC-192, 10GbE Optical Modules System Redundancy/Self Test Clock Fanout

#### **Features**

- ♦ Up to 12.5Gbps Operation

- ♦ Less Than 10psp-p Deterministic Jitter

- **♦ Less Than 0.7psrms Random Jitter**

- ♦ 1.8V, 2.5V, and 3.3V DC-Coupled CML I/O

- **♦ Independent Output Power-Down**

- ♦ 4mm × 4mm Thin QFN Package

- ◆ -40°C to +85°C Operation

- ♦ +3.3V Core Supply

- ♦ 215mW Power Consumption (Excluding **Termination Currents)**

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-<br>PACKAGE | PKG.<br>CODE |

|------------|----------------|-----------------|--------------|

| MAX3841ETG | -40°C to +85°C | 24 Thin QFN     | T2444-1      |

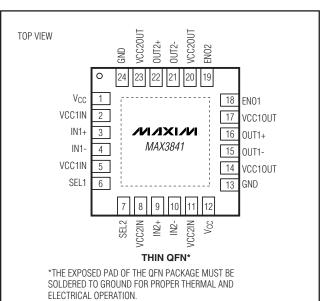

Pin Configuration appears at end of data sheet.

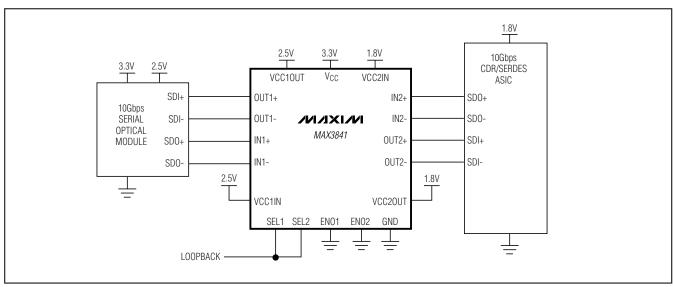

### **Typical Application Circuit**

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VCC              | 0.5V to +4.0V             |

|----------------------------------|---------------------------|

| CML Supply Voltage (VCC_IN, VCC  | C_OUT)0.5V to +4.0V       |

| Continuous Output Current (OUT1± | , OUT2±)±25mA             |

| CML Input Voltage (IN1±, IN2±)   |                           |

| LVCMOS Input Voltage (SEL1, SEL2 | 2,                        |

| ENO1, ENO2)                      | 0.5V to $(V_{CC} + 0.5V)$ |

| Continuous Power Dissipation ( $T_A = +85^\circ$ | °C)            |

|--------------------------------------------------|----------------|

| 24-Pin Thin QFN (derate 20.8mW/°C                |                |

| above +85°C)                                     | 1352mW         |

| Operating Temperature Range                      | 40°C to +85°C  |

| Storage Temperature Range                        | 55°C to +150°C |

| Lead Temperature (soldering, 10s)                | +300°C         |

|                                                  |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{VCC_IN} = +1.71 \text{V to } \text{V}_{CC}, \text{VCC_OUT} = +1.71 \text{V to } \text{V}_{CC}, \text{T}_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}.$  Typical values are at  $\text{V}_{CC} = +3.3 \text{V}, \text{VCC_IN} = \text{VCC_OUT} = 1.8 \text{V}, \text{T}_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                  | SYMBOL                            | CONDITIONS                                          | MIN    | TYP   | MAX    | UNITS             |

|----------------------------|-----------------------------------|-----------------------------------------------------|--------|-------|--------|-------------------|

| Core Supply Current        | Icc                               | Excluding CML termination currents                  |        | 65    | 90     | mA                |

| Data Rate                  |                                   | (Note 1)                                            | 0      |       | 12.5   | Gbps              |

| CML Input Differential     | VIN                               | AC-coupled or DC-coupled (Note 2)                   | 150    |       | 1200   | mV <sub>P-P</sub> |

| CML Input Common Mode      |                                   | DC-coupled                                          | VCC_IN | - 0.3 | VCC_IN | V                 |

| CML Input Termination      |                                   | Single ended                                        | 42.5   | 50    | 57.5   | Ω                 |

| CML Input Return Loss      |                                   | Up to 10GHz                                         |        | 12    |        | dB                |

| CML Output Differential    | Vout                              | (Note 2)                                            | 400    | 500   | 600    | mV <sub>P-P</sub> |

| CML Output Termination     |                                   | Single ended                                        | 42.5   | 50    | 57.5   | Ω                 |

| CML Output Transition Time | t <sub>R</sub> , t <sub>F</sub>   | 20% to 80% (Notes 1, 3)                             |        |       | 30     | ps                |

| Deterministic Jitter       |                                   | (Notes 1, 4)                                        |        |       | 10     | psp-p             |

| Random Jitter              |                                   | V <sub>IN</sub> = 150mV <sub>P-P</sub> (Notes 1, 5) |        | 0.3   | 0.7    | psrms             |

| Propagation Delay          |                                   | Any input to output (Note 1)                        |        | 100   | 140    | ps                |

| Channel-to-Channel Skew    |                                   | (Note 1)                                            |        |       | 12     | ps                |

| Output Duty-Cycle Skew     |                                   | 50% input duty cycle (Notes 1, 3)                   |        |       | 8      | ps                |

| LVCMOS Input Current       | I <sub>IH</sub> , I <sub>IL</sub> |                                                     | -10    |       | +10    | μΑ                |

| LVCMOS Input High Voltage  | VIH                               |                                                     | 1.7    |       |        | V                 |

- Note 1: Guaranteed by design and characterization.

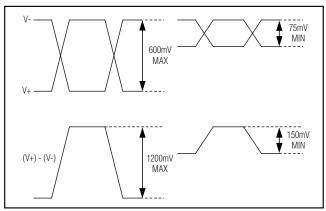

- Note 2: Differential swing is defined as V<sub>IN</sub> = (IN\_+) (IN\_-) and V<sub>OUT</sub> = (OUT\_+) (OUT\_-). See Figure 1.

- **Note 3:** Measured using a 0000011111 pattern at 12.5Gbps, and  $V_{IN} = 400 \text{mV}_{P-P}$  differential.

- Note 4: Measured at 9.953Gbps using a pattern of 100 ones, 27 1 PRBS, 100 zeros, 27 1 PRBS, and at 12.5Gbps using a ±K28.5 pattern. VCC\_IN = VCC\_OUT = 1.8V, and V<sub>IN</sub> = 400mV<sub>P-P</sub> differential.

- Note 5: Refer to Maxim application note HFAN-04.5.1: Measuring Random Jitter on a Digital Sampling Oscilloscope.

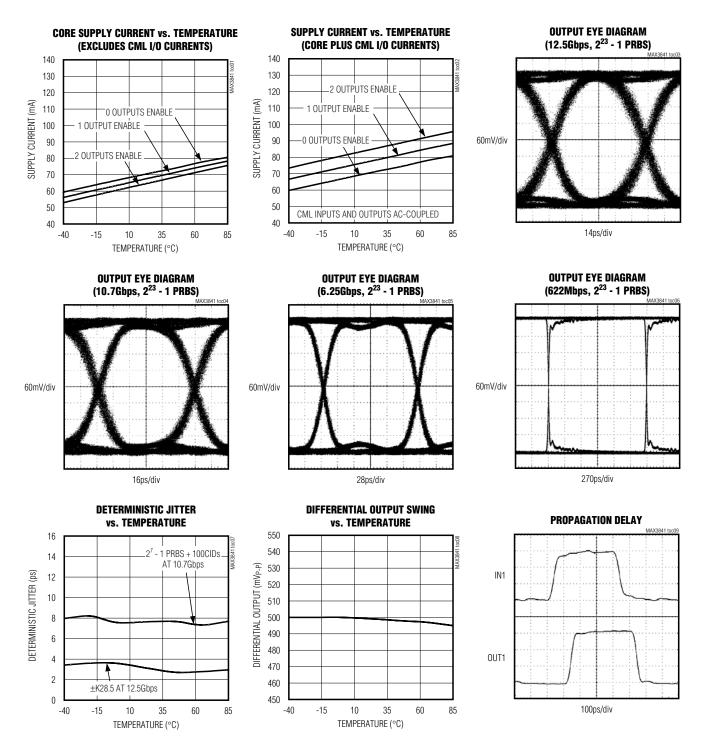

### **Typical Operating Characteristics**

$(V_{CC} = 3.3V, VCC_IN, VCC_OUT = 1.8V, V_{IN} = 500mV_{P-P}, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                            |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------|

| 1, 12  | V <sub>C</sub> C | +3.3V Core Supply Voltage                                                                                           |

| 2, 5   | VCC1IN           | Supply Voltage for CML Input IN1. Connect to 1.8V, 2.5V, or 3.3V.                                                   |

| 3      | IN1+             | Positive Serial Data Input 1, CML                                                                                   |

| 4      | IN1-             | Negative Serial Data Input 1, CML                                                                                   |

| 6      | SEL1             | Output 1 Select, LVCMOS Input. See Table 1.                                                                         |

| 7      | SEL2             | Output 2 Select, LVCMOS Input. See Table 1.                                                                         |

| 8, 11  | VCC2IN           | Supply Voltage for CML Input IN2. Connect to 1.8V, 2.5V, or 3.3V.                                                   |

| 9      | IN2+             | Positive Serial Data Input 2, CML                                                                                   |

| 10     | IN2-             | Negative Serial Data Input 2, CML                                                                                   |

| 13, 24 | GND              | Supply Ground                                                                                                       |

| 14, 17 | VCC10UT          | Supply Voltage for CML Output OUT1. Connect to 1.8V, 2.5V, or 3.3V.                                                 |

| 15     | OUT1-            | Negative Serial Data Output 1, CML                                                                                  |

| 16     | OUT1+            | Positive Serial Data Output 1, CML                                                                                  |

| 18     | ENO1             | Output 1 Enable, LVCMOS Input. See Table 1.                                                                         |

| 19     | ENO2             | Output 2 Enable, LVCMOS Input. See Table 1.                                                                         |

| 20, 23 | VCC2OUT          | Supply Voltage for CML Output OUT2. Connect to 1.8V, 2.5V, or 3.3V.                                                 |

| 21     | OUT2-            | Negative Serial Data Output 2, CML                                                                                  |

| 22     | OUT2+            | Positive Serial Data Output 2, CML                                                                                  |

| EP     | Exposed Pad      | Ground. The exposed pad must be soldered to the circuit board ground for proper thermal and electrical performance. |

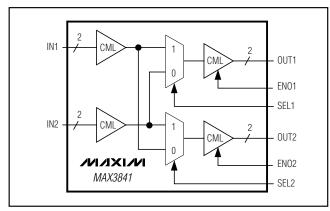

### **Detailed Description**

The MAX3841 contains a pair of CML inputs that drive two 2:1 multiplexers, with separate select inputs SEL1 and SEL2, providing a  $2\times 2$  crosspoint data path. The outputs of the multiplexers each drive a high-performance CML output that can be disabled (powered down) using the ENO1/ENO2 inputs. All of the data paths are fully differential to minimize jitter, crosstalk, and signal skew. See Figure 1 for the functional diagram.

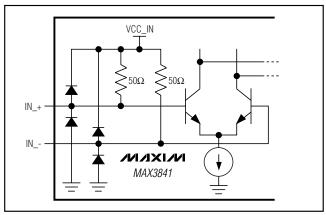

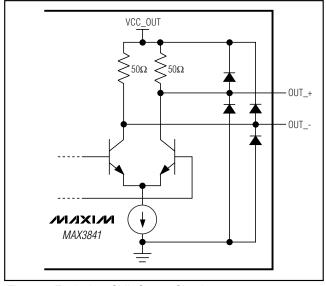

#### **CML Input and Output Buffers**

The MAX3841 input and output buffers are terminated with  $50\Omega$  to independent supply lines, and are also compatible with  $100\Omega$  differential terminations. (See Figures 3 and 4.) Separate power-supply connections are provided for the core, input buffers, and output buffers to allow DC-coupling to 1.8V, 2.5V, or 3.3V CML ICs. If desired, the CML inputs and outputs can be AC-coupled.

The CML inputs accept serial NRZ data with differential amplitude from 150mV<sub>P-P</sub> to 1200mV<sub>P-P</sub> (see Figure 2). The CML outputs provide 500mV<sub>P-P</sub> nominal differential swing, resulting in low power consumption.

Figure 1. Functional Diagram

Figure 2. Definition of Differential Voltage Swing

Figure 3. Equivalent CML Input Circuit

Figure 4. Equivalent CML Output Circuit

### **Table 1. Output Controls**

| ENO1 | ENO2 | SEL1 | SEL2 | OUT1     | OUT2     |

|------|------|------|------|----------|----------|

| 0    | 0    | 0    | 0    | IN2      | IN1      |

| 0    | 0    | 0    | 1    | IN2      | IN2      |

| 0    | 0    | 1    | 0    | IN1      | IN1      |

| 0    | 0    | 1    | 1    | IN1      | IN2      |

| 1    | 1    | Χ    | Χ    | Disabled | Disabled |

### **Applications Information**

#### **Select and Enable Controls**

The MAX3841 provides two LVCMOS-compatible select inputs, SEL1 and SEL2. Either data input can be connected to either or both data outputs. The MAX3841 provides two LVCMOS-compatible enable inputs, ENO1 and ENO2, so each output can be disabled independently. The MAX3841 can also be used as a 1:2 driver, 2:1 multiplexer, or a dual 1:1 buffer by using the LVCMOS control inputs accordingly (see Table 1).

### **Power-Supply Connections**

Each of the input and output power-supply connections (VCC1IN, VCC2IN, VCC1OUT, VCC2OUT) is independent and need not be connected to the same voltage. The input and output supplies can be connected to 1.8V, 2.5V, or 3.3V, but the core supply (VCC) must be connected to 3.3V for proper operation.

#### **Input and Output Interfaces**

The MAX3841 inputs and outputs can be AC-coupled or DC-coupled according to the application. If an input or output is not used it should be terminated with  $50\Omega$  to the correct input or output supply voltage. For more information about interfacing with logic families, refer to Maxim application note HFAN-01.0: *Introduction to LVDS, PECL, and CML*.

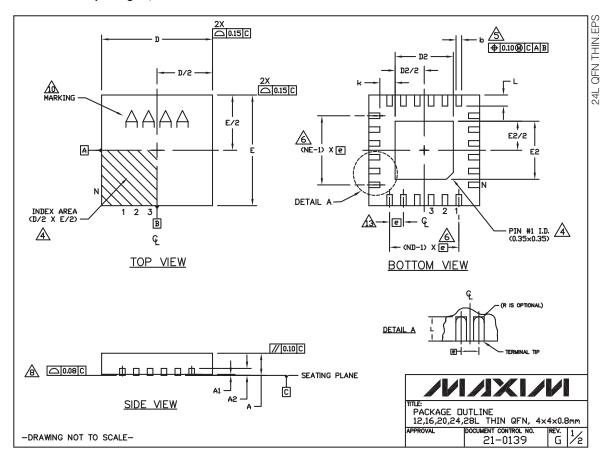

#### **Package and Layout Considerations**

The MAX3841 is packaged in a 4mm × 4mm 24-pin thin QFN with exposed pad. The exposed pad provides thermal and electrical connectivity to the IC and must be soldered to a high-frequency ground plane. Use multiple vias to connect the exposed pad underneath the package to the PC board ground plane.

Use good layout techniques for the 10Gbps PC board transmission lines, and configure the layout near the IC to minimize impedance discontinuities. Power-supply decoupling capacitors should be located as close as possible to the IC.

### Pin Configuration

\_Chip Information

TRANSISTOR COUNT: 950 PROCESS: SiGe BiCMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

|       | COMMON DIMENSIONS |         |        |         |        |         |           |         |           |          |           |      |          |      |      |

|-------|-------------------|---------|--------|---------|--------|---------|-----------|---------|-----------|----------|-----------|------|----------|------|------|

| PKG   | 12L 4×4           |         |        | 16L 4×4 |        | 20L 4×4 |           | 24L 4×4 |           | 28L 4×4  |           |      |          |      |      |

| REF.  | MIN.              | NDM.    | MAX.   | MIN.    | NOM.   | MAX.    | MIN.      | NOM.    | MAX.      | MIN.     | NDM.      | MAX. | MIN.     | NDM. | MAX. |

| Α     | 0.70              | 0.75    | 0.80   | 0.70    | 0.75   | 0.80    | 0.70      | 0.75    | 0.80      | 0.70     | 0.75      | 0.80 | 0.70     | 0.75 | 0.80 |

| A1    | 0.0               | 0.02    | 0.05   | 0.0     | 0.02   | 0.05    | 0.0       | 0.02    | 0.05      | 0.0      | 0.02      | 0.05 | 0.0      | 0.02 | 0.05 |

| A2    | (                 | .20 RE  | F      | 0       | .20 RE | F       | 0.20 REF  |         | 0         | 0.20 REF |           |      | 0.20 REF |      |      |

| b     | 0.25              | 0.30    | 0.35   | 0.25    | 0.30   | 0.35    | 0.20      | 0.25    | 0.30      | 0.18     | 0.23      | 0.30 | 0.15     | 0.20 | 0.25 |

| D     | 3.90              | 4.00    | 4.10   | 3.90    | 4.00   | 4.10    | 3.90      | 4.00    | 4.10      | 3.90     | 4.00      | 4.10 | 3.90     | 4.00 | 4.10 |

| E     | 3.90              | 4.00    | 4.10   | 3.90    | 4.00   | 4.10    | 3.90      | 4.00    | 4.10      | 3.90     | 4.00      | 4.10 | 3.90     | 4.00 | 4.10 |

| е     |                   | 0.80 BS | C.     | 0       | .65 BS | C.      | 0.50 BSC. |         | 0.50 BSC. |          | 0.40 BSC. |      |          |      |      |

| k     | 0.25              | -       | -      | 0.25    | -      | -       | 0.25      | -       | -         | 0.25     | -         | -    | 0.25     | -    | -    |

| L     | 0.45              | 0.55    | 0.65   | 0.45    | 0.55   | 0.65    | 0.45      | 0.55    | 0.65      | 0.30     | 0.40      | 0.50 | 0.30     | 0.40 | 0.50 |

| N     |                   | 12      |        | 16      |        | 20      |           | 24      |           | 28       |           |      |          |      |      |

| ND    |                   | 3       |        | 4       |        | 5       |           | 6       |           | 7        |           |      |          |      |      |

| NE    |                   | 3       |        |         | 4      |         | 5         |         | 6         |          | 7         |      |          |      |      |

| Jedec | VGGB VGGC         |         | WGGD-1 |         | VGGD-2 |         |           | WGGE    |           |          |           |      |          |      |      |

| EXPOSED PAD VARIATIONS |           |      |      |      |      |      |  |  |  |

|------------------------|-----------|------|------|------|------|------|--|--|--|

| PKG.                   |           | D2   |      | E2   |      |      |  |  |  |

| CODES                  | MIN. NOM. |      | MAX. | MIN. | NDM. | MAX. |  |  |  |

| T1244-3                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T1244-4                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T1644-3                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T1644-4                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T2044-2                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T2044-3                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T2444-2                | 1.95      | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |

| T2444-3                | 2.45      | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |

| T2444-4                | 2.45      | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |

| T2844-1                | 2.50      | 2.60 | 2.70 | 2.50 | 2.60 | 2.70 |  |  |  |

#### NOTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- ALL DIFFERSIONS FRE IN FILE THE LEGS. HOLES AND STATE OF TERMINALS.

A. N IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION 16 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP.

- AND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

ACCUPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- 9. DRAWING CONFORMS IN JEDEC MICEO, EACH FOR THE MARKING IS FOR PACKAGE DRIENTATION REFERENCE ONLY.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm.

- 12. WARPAGE SHALL NOT EXCEED 0.10mm.

12. WARPAGE SHALL NOT EXCEED 0.10mm.

13. LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 15. ALL DIMENSIONS ARE THE SAME FOR LEADED (-) & POFREE (+) PACKAGE CODES.

PACKAGE DUTLINE 12,16,20,24,28L THIN QFN, 4×4×0.8mm DOCUMENT CONTROL NO. REV. 2/2 21-0139

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.